## TRABAJO ESPECIAL DE GRADO

### DESARROLLO DE UN SISTEMA DE PROCESAMIENTO DE IMÁGENES PARA MICROSATÉLITES

Profesor Guía: Tremante Panayotis Tutor Industrial: Claudio Passerone

> Presentado ante la Ilustre Universidad Central de Venezuela por el Br. Alejandro G. González E. para optar al Título de Ingeniero Electricista

Caracas, 2009

# CONSTANCIA DE APROBACIÓN

Caracas, 2009

Los abajo firmantes, miembros del Jurado designado por el Consejo de Escuela de Ingeniería Eléctrica, para evaluar el Trabajo Especial de Grado presentado por el Bachiller Alejandro Gabriel González Esculpi, titulado:

# "DISEÑO DE UN SISTEMA DE PROCESAMIENTO DE IMÁGENES PARA MICROSATÉLITES"

Consideran que el mismo cumple con los requisitos exigidos por el plan de estudios conducente al Título de Ingeniero Electricista en la mención de Electrónica, y sin que ello signifique que se hacen solidarios con las ideas expuestas por el autor, lo declaran APROBADO.

her

Jurado

n

emante

Profesor Guía

### González E., Alejandro G.

### DESARROLLO DE UN SISTEMA DE PROCESAMIENTO DE IMÁGENES PARA MICROSATELITES

Prof. Guía: Tremante Panayotis. Tutor Industrial: Claudio Passerone. Tesis. Caracas. U.C.V. Facultad de Ingeniería. Escuela de Ingeniería Eléctrica. Ingeniero Electricista. Opción: Electrónica. Institución: Politécnico de Turín. Turín, Italia. 2009. 95 h. + anexos.

**Palabras Claves**: Satélite; Procesamiento de imágenes; Procesador; VHDL; FPGA; Sistema Operativo; Programas.

**Resumen**. Se plantea el estudio y desarrollo de una propuesta para un sistema de procesamiento de imágenes como eventual Payload de un satélite universitario basado en el estándar CUBESAT. Se toma como punto de partida el modelo VHDL sintetizable de un procesador el cual puede servir de base a un sistema operativo compilable, capaz de sostener programas para el procesamiento de imágenes. Para el desarrollo del proyecto fue provista una tarjeta de bajo consto basada en un chip FPGA capaz de sostener el procesador mencionado así como varios periféricos útiles para la realización de diversas pruebas sobre el mismo.

# Sumario

La simplicidad del estándar CubeSat para el diseño de picosátelites, definido en el año 2001 por el Profesor Robert Twiggs de la Universidad de Stanford en EE.UU., ha motivado varias universidades a nivel mundial a desarrollar sistemas de esta categoría como actividad didáctica, capturando además el interés de diversos sectores a invertir en el desarrollo de investigaciones en el campo de las telecomunicaciones.

El satélite PICPOT fue desarrollado en el Politécnico di Torino desde el 2003, sirviendo como primera experiencia para la institución y motivando futuros proyectos en el mismo campo. Así en el año 2006 nace el proyecto ARAMIS, segundo satélite del Politécnico di Torino, actualmente en pleno desarrollo.

La peculiaridad del proyecto ARAMIS es la "modularidad", es decir, el desarrollo independiente y simultaneo de diversos módulos estándar compatibles entre sí, en lugar de ser orientado al cumplimiento de una misión particular. Los principales módulos o etapas que constituyen el proyecto ARAMIS son: Etapa de Potencia, Etapa de transmisión y recepción, Computador de Bordo, Estación de Tierra y Payload.

Este trabajo está orientado al estudio y desarrollo de una propuesta para un eventual Payload dedicado a la adquisición de imágenes. Se toma como punto de partida el modelo VHDL sintetizable de un procesador el cual puede servir de base a un sistema operativo compilable, capaz de sostener programas para el procesamiento de imágenes. Para el desarrollo del proyecto fue provista una tarjeta de bajo consto basada en un chip FPGA capaz de sostener el procesador mencionado así como varios periféricos útiles para la realización de diversas pruebas sobre el mismo.

La tarjeta utilizada es la GR-XC3S-1500 construida por Pender en colaboración con Gaisler Reseach, basada en una FPGA Spartan 3, conteniendo como principales periféricos memorias PROM y puertos: seriales, Ethernet, USB, JTAG, y VGA.

El modelo VHDL utilizado corresponde al procesador LEON3, desarrollado por Gaisler Research basado en la arquitectura SPARC V8, especialmente diseñado para aplicaciones satelitales. La librería GRLIB IP esta también incluida en el modelo, conteniendo dispositivos útiles y en algunos casos indispensables para el procesador. También son provistas por la Gaisler varias herramientas que simplifican la configuración del modelo VHDL antes de la síntesis y para la compilación de aplicaciones a ser ejecutadas en el procesador.

Para la síntesis del modelo VHDL y su instalación en la FPGA (utilizando un cable JTAG) son utilizadas aplicaciones contenidas en el paquete ISE Foundation de Xillinx. Para probar el procesador instalado se utilizó una versión de prueba de GRMON, un programa que sirve de interfaz para procesadores LEON a través de los puertos JTAG, serial o USB; permitiendo controlar los dispositivos instalados junto al procesador, la instalación y ejecución de aplicaciones, así como otros aspectos importantes del sistema.

Varios fallos fueron observados en el procesador obtenido del modelo VHDL sintetizado con las herramientas disponibles (inclusive utilizando la configuración default para el modelo) el cual hizo imposible su utilización. Por ende se decidió utilizar una versión ya sintetizada del procesador también provisto por la Gaisler, la cual funcionó en la tarjeta de manera óptima, permitiendo descartar posibles daños físicos como causa de los fallos previamente obtenidos. Se decidió continuar el proyecto utilizando la versión operativa del procesador en lugar de intentar corregir la versión configurable, permitiendo probar la capacidad del procesador más allá de no poder demostrar la flexibilidad del modelo VHDL. Se utilizó SnapGear Linux como sistema operativo a ser instalado en el procesador, el paquete escogido incluye el kernel correspondiente, herramientas para simplificar su configuración y diversos templates ente los cuales uno corresponde al procesador LEON3 en la tarjeta GR-XC3S-1500, las modificaciones realizadas al kernel fueron limitadas a la asignación de la dirección IP y la instalación de programas a ser ejecutados de forma automática en la tarjeta.

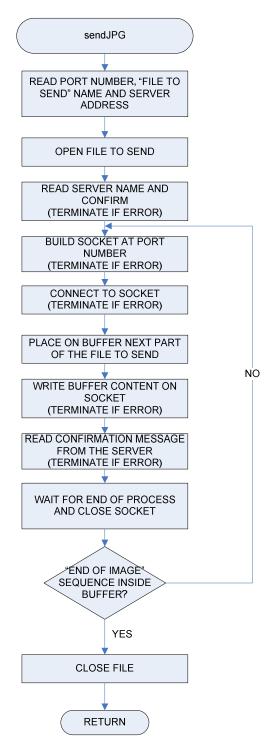

Para probar la adquisición y envío de datos se utilizó el puerto Ethernet, aprovechando el protocolo TCP/IP y desarrollando programas basados en el modelo Cliente-Servidor para el intercambio de datos entre la tarjeta y bloques externos del sistema emulados por diversos procesos en un servidor externo. Para probar la capacidad del procesador para el procesamiento de imágenes se utilizó la librería JPEG elaborada por IJG (Independent JPEG Group), la cual incluye archivos en lenguaje C en formato open-source, open-license, conteniendo códigos fuente de programas que hacen la compresión basada en el algoritmo correspondiente. Se decidió trabajar con archivos en formato PPM para ser comprimidos y obtener los archivos correspondientes en formato JPEG.

La última parte del proyecto consistió en el desarrollo de programas que incluyen en el modelo Cliente-Servidor, los tipos de archivo utilizados y las funciones para la compresión. Los programas desarrollados fueron los siguientes:

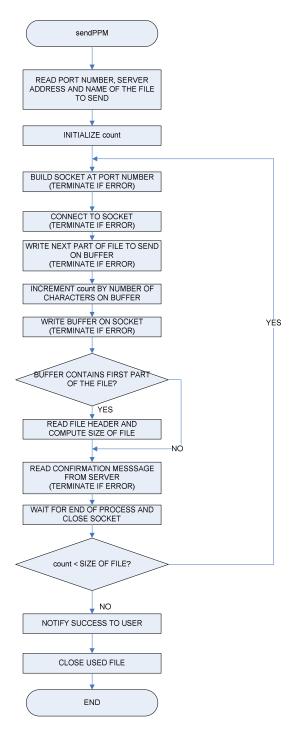

- sendPPM: envía un archivo en formato PPM del servidor a la tarjeta.

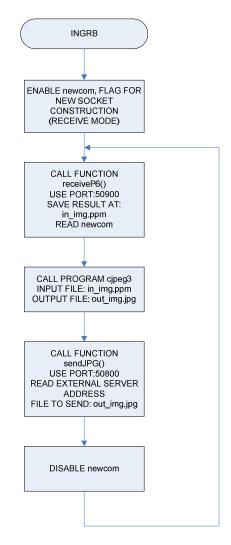

- INGRB: corre en la tarjeta de forma constante, esperando por un archivo PPM a ser comprimido, ejecuta el programa para la compresión al recibirlo, envía el archivo JPEG obtenido y espera por el siguiente archivo PPM.

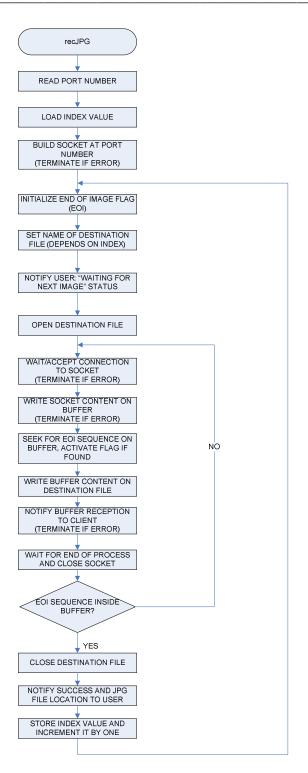

- recJPG: corre en el servidor de manera constante, recibe el archivo JPEG enviado desde la tarjeta y lo almacena en memoria.

La compresión es realizada por el programa cjpeg3, el cual es el mismo cjpeg provisto por la librería de IJG, con ligeras modificaciones en su código fuente. Los resultados obtenidos fueron satisfactorios, se utilizaron varios archivos PPM y fueron medidos los tiempos obtenidos para el envío, la compresión y la recepción de archivos correspondientes para cada caso.

El trabajo presentado se organiza de la manera siguiente:

- Capitulo 1: introducción sobre los satélites universitarios, descripción de aspectos del proyecto ARAMIS.

- Capitulo 2: describe el desarrollo del hardware (posicionamiento del procesador sobre la tarjeta).

- Capitulo 3: describe el desarrollo del sistema operativo (compilación del kernel y cambios realizados)

- Capitulo 4: describe el desarrollo de programas para el envío y recepción de datos, y el procesamiento de imágenes.

- Capitulo 5: conclusiones.

# Contents

| Co                         | onstancia de aprobación                           | iii |

|----------------------------|---------------------------------------------------|-----|

| Re                         | esumen                                            | iv  |

| Su                         | ımario (en castellano)                            | v   |

| Co                         | ontents                                           | ix  |

| List of Figures and Tables |                                                   | xi  |

| 1.                         | Introduction                                      | 1   |

|                            | 1.1. The PICPOT project                           | 2   |

|                            | 1.2. The ARAMIS project                           | 4   |

| 2.                         | Hardware Implementation                           | 6   |

|                            | 2.1. The LEON3 Processor Core                     | 6   |

|                            | 2.1.1. LEON3 Architecture and Features            | 7   |

|                            | 2.1.2. The GRLIB IP Library                       | 9   |

|                            | 2.1.3. LEON3 Applications development tools       | 10  |

|                            | 2.2. The GR-XC3S-1500 Development Board           | 11  |

|                            | 2.2.1. Board technical description                | 13  |

|                            | 2.2.2. Board parts to be used                     | 16  |

|                            | 2.3. LEON3 Design Configuration                   | 20  |

|                            | 2.4. Procedure to place the processor on the FPGA | 22  |

|                            | 2.5. The GRMON LEON Monitor                       | 24  |

|                            | 2.6. Tests and Results                            | 25  |

| 3.                         | Firmware Implementation                           | 29  |

|                            | 3.1. The SnapGear Linux                           | 29  |

|                            | 3.2. SnapGear Linux Compiling                     | 30  |

|                            | 3.2.1. Installing the Toolchain                   | 31  |

|                            | 3.2.2. Installing the SnapGear Distribution       | 32  |

|                            | 3.2.3. Configuring Linux                          | 32  |

|                            | 3.2.4. Building SnapGear                          | 37  |

|                            | 3.3. Modifications over the SnapGear Linux Kernel | 37  |

|    | 3.3.1. Board IP address                             | 37 |

|----|-----------------------------------------------------|----|

|    | 3.3.2. Adding programs to be executed on the board  | 38 |

|    | 3.3.3. Automatic Program Startup                    | 39 |

|    | 3.4. SnapGear Linux Installing Procedure            | 40 |

|    | 3.5. Tests and Results                              | 42 |

| 4. | Software Implementation                             | 48 |

|    | 4.1. Used File Formats                              | 48 |

|    | 4.1.1. PPM file format                              | 49 |

|    | 4.1.2. JPEG file format                             | 51 |

|    | 4.2. An Overview of the JPEG Compression Algorithm  | 53 |

|    | 4.3. The IJG JPEG Library                           | 57 |

|    | 4.4. Communication Channel Development              | 58 |

|    | 4.4.1. The Client-Servr model                       | 58 |

|    | 4.4.2. Socket Types                                 | 58 |

|    | 4.4.3. Socket implementation on the Internet domain | 59 |

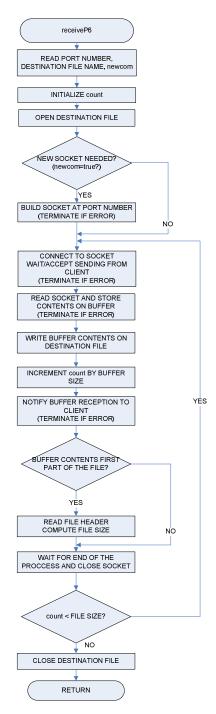

|    | 4.5. Developed Program Description                  | 67 |

|    | 4.5.1. To run outside the Board                     | 67 |

|    | 4.5.2. To run Inside the Board                      | 69 |

|    | 4.6. Developed Programs Usage                       | 77 |

|    | 4.7. Tests and Results                              | 79 |

| 5. | Conclusions                                         | 81 |

| Bi | bliography                                          | 84 |

| Ap | opendixes                                           | 86 |

|    | A.Developed Programs Source Codes                   | 86 |

# List of Figures and Tables

| Figure 1.1. The PICPOT Satellite                              | 3  |

|---------------------------------------------------------------|----|

| Figure 2.1. LEON3 processor core block diagram                | 7  |

| Figure 2.2. The GR-XC3S-1500 Development Board                | 11 |

| Figure 2.3. GR-XC3S-1500 development board block diagram      | 13 |

| Figure 2.4. Board Memory Interface                            | 16 |

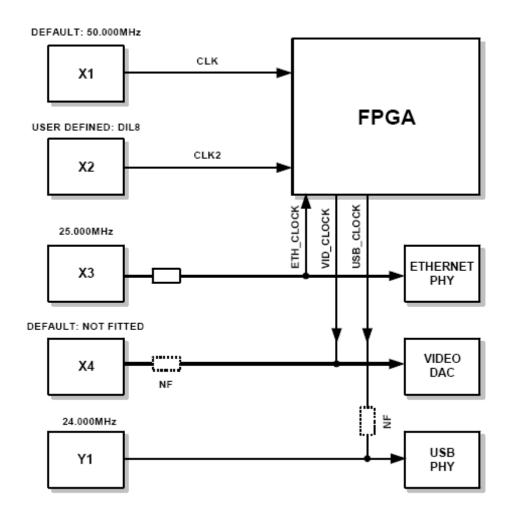

| Figure 2.5. Configuration of Oscilators                       | 18 |

| Figure 2.6. LEON3 GUI configuration tool                      | 20 |

| Figure 2.7. Processor configuration window                    | 21 |

| Figure 2.8. Peripherals configuration window                  | 21 |

| Figure 2.9. Built LEON3 processor on GRMON monitor            | 25 |

| Figure 2.10. Failures on the built processor                  | 26 |

| Figure 2.11. Precompiled LEON3 processor on GRMON monitor     | 27 |

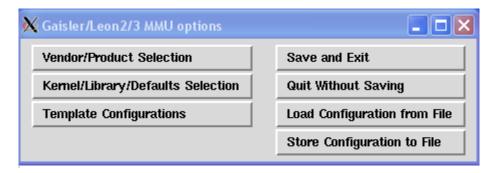

| Figure 3.1. SnapGear main configuration GUI                   | 32 |

| Figure 3.2. Template Configuration selection                  | 33 |

| Figure 3.3. Vendor/Product section                            | 34 |

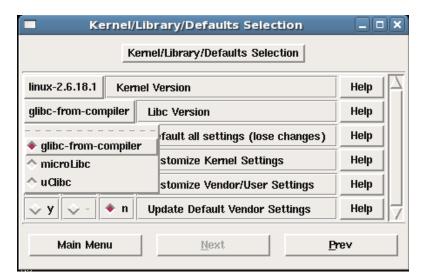

| Figure 3.4. kernel/library/defaults selection menu            | 34 |

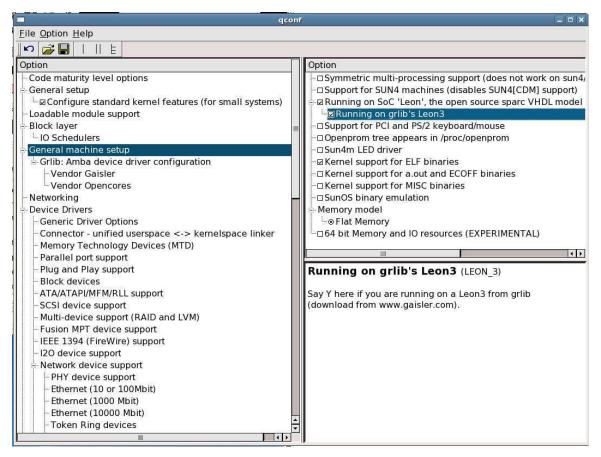

| Figure 3.5. Linux 2.6.x kernel GUI configuration utilit       | 35 |

| Figure 3.6. Board IP address setting                          | 38 |

| Figure 3.7. Example of the inittab file                       | 39 |

| Figure 3.8.Flash erasing and SnapGear image download on GRMON | 43 |

| Figure 3.9. Programs and files added to the root file system  | 44 |

| Figure 3.10. Board IP address verification from a remote host | 44 |

| Figure 3.11. Board IP address verification on SnapGear shell  | 45 |

| Table 4.1. PPM formats comparison                             | 50 |

| Table 4.2. JPEG markers                                       | 52 |

| Figure 4.1 Server side socket building and usage              | 60 |

| Figure 4.2. Client side socket building and usage             | 64 |

| Figure 4.3. sendPPM program flow chart    | 72 |

|-------------------------------------------|----|

| Figure 4.4. recJPG program flow chart     | 73 |

| Figure 4.5. INGRB program flow chart      | 74 |

| Figure 4.6. receiveP6 function flow chart | 75 |

| Figure 4.7. sendJPG function flow chart   | 76 |

| Figure 4.8. Programs test environment     | 79 |

| Table 4.3. Programs performance           | 80 |

# **Chapter 1**

# Introduction

Issued on the year 2001, the CUBESAT (cube satellite) [1] standard has inspired many universities worldwide to invest several research efforts into the development of aerospace applications based on that model. The standard has been developed under the guidance of Professor Robert Twiggs (from Stanford University, USA) in association with the Space Systems Development Laboratory (SSDL) from Stanford University and California Polytechnic State University.

The CUBESAT standard is basically defined by the following characteristics:

- Volume: 10x10x10cm

- Weight: < 1kg

Compared to traditional multi-million-dollar satellite missions, CubeSat projects have the potential to educate the participants and implement successful and useful missions in science and industry at much lower costs.

Inspired on the CUBESAT model, Politecnico di Torino has recently developed the PICPOT satellite [2], and now the ARAMIS project is under development.

### **1.1 The PICPOT Project**

PICPOT [2] was the first satellite developed at Politecnico di Torino. It development began on 2003 and its launch failed on 2006[]. The project was based on the following requierements:

- Cube shape, 13x13x13cm

- Weight: < 5kg

- Medium Power < 1.5 W

- Minimum lifetime: 90 days

- COTS components usage in space

- LEO Orbit (altitude between 600 and 800km)

- Compatibility with the POD launcher

The functions of the satellite regarded the following parameters:

- Temperature and luminescence measures acquisition

- Photographies acquisition

- Data transfer to the ground station

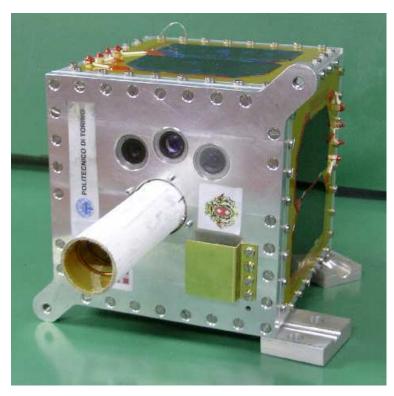

A PICPOT picture is presented in figure 1.1

### 1 - Introduction

Figure 1.1. The PICPOT satellite

Five of the six satellite faces were used to place the solar panels. On the remaining face two antennas (437MHz and 2.4GHz), 3 cameras, 2 kill switches and a test connector to verify the on-board electronics correct functioning were placed. Internal power supply was provided by 6 rechargeable batteries placed between the solar cells and the electronic boards. Three processors were placed on the satellite:

- ProcA: on-board management, associated to the 437MHz communication channel, 11MHz clock frequency and power supply of 3.3V.

- ProcB: on-board management associated to the 2.4GHz communication channel, 4MHz clock frequency and power supply of 3.3V

- Payload: for the image acquisition from the three photocameras, send to ground station by ProcA and ProcB.

ProcA and ProcB were operationally independent. The communication with the ground station was designed to be performed through two channels, both of them in amateur band with APRS protocol.

### **1.2 The ARAMIS Project**

The ARAMIS project has assumed the PICPOT project evolution. The ARAMIS target is to define a low cost standard modular architecture for small size satellites. The applied "modular architecture" [3] method aims to develop some standard modules connectable between them and with specific modules built according to the mission, rather than develop the entire system based on the mission. The standard modules to be developed are listed as follows:

- Power Supply (Power Management tile)

- Tx-Rx (Telecommunication tile)

The modules which complete the satellite system and are developed according to the required mission are:

- Ground Station

- On Board Computer

- Payload

This procedure allows also fix the number of standard modules according of each kind to the satellite mission. The main feature of the modular architecture model is the re-usability of the designs involved in the standard modules; this factor is translated as saving of a high amount of resources and time in future projects.

The main target of the presented project in this thesis is to develop a proposal for an eventual Payload processor oriented to image acquisition. The starting point is a processor defined by a provided VHDL model able to support an operating system, which should be able to support applications that manage the activities related to procedures in image processing. It is provided a development board specially designed for the mentioned processor support.

# **Chapter 2**

# **Hardware Implementation**

This chapter explains the procedure to compile a processor open-source VHDL model and place it over a based-on FPGA development board. After the compiling is completed and the processor is placed on the board, are discussed the results of some tests performed over it to prove its operation, the flexibility of the used model and the reliability of the development board itself. The built processor is also compared with a precompiled version provided by the manufacturer.

### 2.1 The LEON3 Processor Core

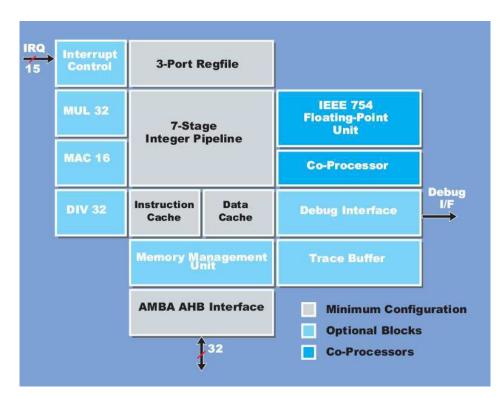

The LEON3 [4,6] processor core is a synthesizable VHDL model of a 32-bit processor with the SPARC V8 architecture. The core is highly configurable and suitable for system-on-a-chip (SOC) designs. The configurability allows designers to optimize the processor for performance, power consumption, I/O throughput, silicon area and cost. The core is interfaced using AMBA-2.0 AHB bus, and supports the IP plug and play method provided in the Gaisler Research IP Library (GRLIB). The Processor can be efficiently on both FPGA and ASIC technologies and uses standard synchronous RAM cells for both caches and register file. To promote the SPARC architecture and simplify early evaluation and prototyping, the processor and associated IP library is provided in full source code under open-source license. The LEON3 processor core block diagram is shown in figure 2.1.

Figure 2.1. LEON3 processor core block diagram

The LEON3 core is also available in a fault-tolerant version (LEON3FT) immune to single event upsets (SEUs), for space and other high-rel applications. The fault tolerant version is not provided under open-source license, but it supports most of the functionality in the standard LEON3 perocessor.

### 2.1.1 LEON3 Architecture and features

LEON3 [4,6] is implemented using an advanced 7-stage pipeline with separate instruction and data cache buses (Harvard architecture). The processor supports the full SPARC V8 instruction set, including the MUC, MAC and DIV instructions. An optional IEEE-754 floating-point unit (FPU) provides support for both single- and double-precision floating point operations. The cache system supports multi-set caches with up to 4 sets per cache, 256 kbyte per set and a choice of LRU, LRR or random replacement policy.

LEON3 can be utilized in synchronous multiprocessor configurations (SMP), and provides hardware support for cache coherency, processor enumeration and SMP interrupt steering. A unique debug interface allows non-intrusive hardware debugging of both single- and multi-processor systems, and provides access to all on-chip registers and memory. Trace buffers for both instructions and AMBA bus traffic are also available.

The basic processor core (pipeline, cache controllers and AHB interface) consumes around 20,000 gates and can be implemented on both ASIC and FPGA technologies. On a typical 0.13  $\mu$ m standard-cell technology, over 400 MHz can be reached.

The LEON3 processor features are resumed in the following list:

- SPARC V8 integer unit with 7-stage pipeline

- Hardware multiply, divide and MAC units

- Interface to the Meiko FPU and custom co-processors

- Interface to high performance IEEE-754 FPU

- Separate instruction and data cache

- Set-associative caches: 1 4 sets, 1 256 kbytes/set. Random, LRR or LRU replacement

- Data cache snooping

- On-chip 0-waitstate scratch pad data RAM

- SPARC V8 Reference Memory management unit (MMU)

- Power-down mode

- Advanced on-chip debug support unit and instruction trace buffer

- AMBA-2.0 AHB and APB on-chip buses

#### 2.1.2 The GRLIB IP Library

To achieve optimum performance and minimum cost for a SOC design, it is important to reuse existing IP cores and be able to configure these cores for the specific application. The GRLIB IP Library [6] provides a standardized and vendorindependent infrastructure to deliver reusable IP cores.

Integrating third party IP cores form different suppliers can require significant adaptation and harmonization of both functional and logistical interfaces. The GRLIB IP library enhances the development of SOC devices by providing reusable IP cores with common functional and logistical interfaces.

The library is designed to be easy portable to different CAD tools and target technologies. It does not depend on any vendor specific interface or technology which needs to be licensed or procured. The library is designed to allow contributions or extensions from other parties. The GRLIB is designed to be "bus-centric", i.e., under the assumption that most of the IP cores will be connected through an on-chip bus (such as AMBA-2.0, AHB/APB).

The GRLIB library contains the following IP cores:

- AHB arbiter/multiplexer with plug&play support

- AHB/APB bridge

- 8/16/32-bits PROM and SRAM controller

- 32-bits PC133 SDRAM controller

- UART, timer unit, interrupt controller and GPIO port

- AHB trace buffer

- 32-bit Initiator/Target PCI interface (FIFO/DMA)

- PCI trace buffer

- 10/100 Mbit Ethernet MAC

- Fully pipelined single- and double- precision IEEE-754 FPU

- Technology-independent memory and pad wrappers

### 2.1.3 LEON3 Applications development tools

Many open source software tools are available for LEON3 applications development [3,6]. A package based on a GNU cross-compilation system is provided by Gaisler Research, including the following tools:

- GNU C/C++ compiler

- Linker, assembler, archiver etc.

- Standalone C-library

- RTEMS real-time kernel with network support

- Boot-prom utility (mkprom)

- Remote debugger monitor for gdb

- GNU debugger with Tk front-end

- DDD graphical user interface for gdb

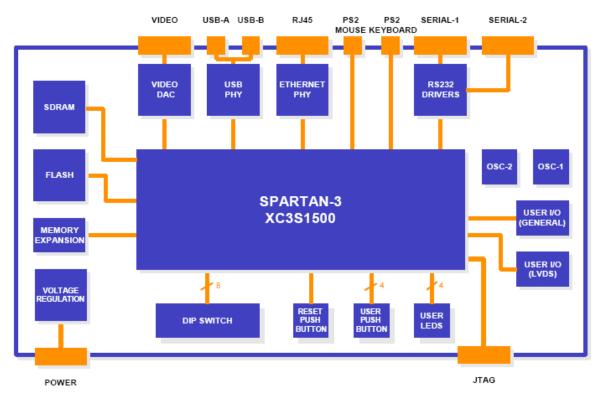

## 2.2 The GR-XC3S-1500 Development Board

The GR-XC3S board [5] is a compact, low-cost development board which has been developed by Pender Electronic Design in cooperation with Gaisler Research to enable the evaluation of the LEON2 and LEON3/GRLIB processor systems. The board incorporates a 1.5 million gate XC3S1500 FPGA device from the Xilinx Spartan3 family, which is supported by the free Xilinx web-pack synthesis and place and route tools.

On-board Flash memory and SDRAM are provided together with Ethernet, JTAG, Serial, Video, USB and PS2 interfaces for off-board communication. The incorporation of the onboard volatile and non-volatile memory, together with the communication interfaces makes the board ideal for fast prototyping, evaluation and development of software for Leon microprocessor applications. An actual picture of the board is provided in figure 2.2.

Figure 2.2. The GR-XC3S-1500 Development Board

Expansion to user's peripherals and circuits can be implemented using the expansion connectors, either to implement a user defined mezzanine board, or via ribbon cable connections. A specific connector is provided to allow connection to the standard memory bus signals.

Although targeted for the development of small Leon based systems and computer peripherals, this board can easily be used as a general purpose FPGA development environment for any Xilinx Spartan-3 design.

The board technical description and selection of parts to be used are described as follows.

#### 2.2.1 Board technical tescription

As previously said, the GR-XC3S-1500 development board incorporates a large capacity Xillinx Spartan-3 FPGA, with on-board memory and interfaces. The board provides a platform which enables the implementation of complex FPGA designs, specially to LEON processors based systems. The development board block diagram is presented in figure 2.3.

Figure 2.3. GR-XC3S-1500 development board block diagram

The features of the GR-XC3S-1500 Development Board are as follows [ref2]:

- Compact Eurocard (100x160mm) size stand-alone operation with +5V power input

- Xilinx XC3S1500-4FG456 FGPA

- o 1.5million gate Xilinx Spartan 3 device in 456 BGA package

- 1 x 4Mbit (XCF04S) and 1 x 1Mbit (XCF01S) platform Flash Proms for non-volatile storage of FPGA configuration

- On-Board Power Regulators

Texas Instruments TPS75003 Triple-Supply Power Management IC providing

- o +3.3V i/o voltage

- o +2.5V auxiliary voltage

- o +1.2V core voltage

- On-Board Memory

- o PROM 64 Mbit (8 Mbyte) FLASH (organised x8 or x16 bit)

- SDRAM 512 Mbit (64 Mbyte) PC-133 SDRAM on board (32 bits wide interface)

- SRAM memory can be added via Mezzanine board, using the memory expansion connector.

- On-Board Oscillators

- Main oscillator 50MHz

- o User fitted oscillator (DIL-8 socketed)

- o Ethernet oscillator 25MHz

- Interfaces

- Serial interfaces: Texas Instruments SN75C3232, 3-V To 5.5-V Multichannel RS-232 Compatible Line Driver/Receivers providing high speed serial interfaces (1 Mbaud RS232) with two standard SUB-D9 female connector interfaces. Can easily be configured to support LEON serial DSU for processor debug and program download

- Ethernet PHY: Intel LXT971A 3.3V Dual-Speed Fast Ethernet PHY Transceiver device providing 10/100Mbit/s Ethernet interface, with RJ45 10/100Mbit Ethernet connector

- Video DAC: Analog Devices ADV7125-50 Triple 8 bit High-Speed Video DAC device, providing 50MHz, 24 bit Video DAC interface for driving a standard 15 pin VGA type connector interface

- USB: Cypress CY7C68000 USB 2.0 UTMI Transceiver connecting to either USB-A (Host) or USB-B (Peripheral) style connectors for USB 2.0 interfaces

- PS2 Mouse and Keyboard: Two PS2 style connectors providing standard PS2 style interfaces (e.g. Mouse and Keyboard)

- JTAG: Connectors supporting both Parallel Cable III (Flying leads) and Parallel cable IV (2x7pin 2mm header) for JTAG programming and configuration download to FPGA

- Memory expansion connector: 120 pin expansion connector: AMP 177-984-5, allowing connection to mezzanine board or to a logic analyser with appropriate adapter

- User I/O's

- LVDSIO: One 2 x 20 pin 0.1" header providing 12 LVDS signal pairs for User defined signals. Can also be configured and used as 24 standard LVTTL/LVCMOS single ended I/O signals for user defined signals

- GENIO: Three 2 x 20 pin 0.1" headers, each providing 20 user definable I/O signals (total 60 user defined signals)

- PIO: 16 bit PIO port accessible via expansion connector (20 pin 0.1" header), compatible with existing GR-PCI accessory products to provide easy expansion of optional 2 x RS232 / 2 x RS422 / 2 x LVDS or 2 x CANBUS interfaces. Can also be configured to provide 16 user defined I/O signals

- Switches

- o 8 pole DIP switch for User Definable functions

- o Two user definable push-button switches

- One push-button switch for system reset and one push-button switch for FGPA (re)configuration

- Indicators

Four User definable LED indicators.

- o One indicating power on board

- One indicating FPGA programming status

- o One indicating Prom-busy

- o One indicating USB current fault

### 2.2.2 Board parts to be used

The parts of the development board used in the project beside the FPGA are explained with some detail as follows.

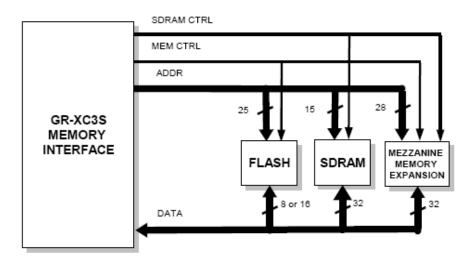

• Memory Organization

The *GR-XC3S-1500* provides FLASH (PROM) memory and SDRAM on board, providing the necessary memory control and Address/Data signals. The memory organisation on the *GR-XC3S-1500* board is represented in Figure 2.4.

Figure 2.4. Board Memory Interface

- PROM 64 Mbit (8 Mbyte) FLASH (organised x8 or x16 bit)

- SDRAM 512 Mbit (64 Mbyte) PC-133 SDRAM on board (32 bits wide interface)

The provided mezzanine memory expansion is not used in this project. The address, data and standard memory control signals (MEM CTRL) are made available for external use on the J9 expansion connector.

The FLASH memory is normally not write protected. However, if a zero-ohm resistor is installed for JP1, the FLASH memory can be configured to protected it from Write/Erase operations. When writing or block-erasing the FLASH memory, LED D12 will illuminate. The FLASH memory normally operates in 8bit wide memory mode. However, if a zero-ohm resistor is installed for JP2, the FLASH memory can be configured to instead operate in 16 bit data mode.

• Oscillators

A number of oscillators are provided on the *GR-XC3S-1500* board as represented in Figure 2.5.

Figure 2.5. Configuration of Oscilators

The main oscillator (*CLK*) for the GR-XC3S-1500 device is 50MHz precision oscillator, X1. A DIL8 socket is provided in order to allow the user to install their own user defined oscillator to provide *CLK2* if required.

The Ethernet PHY requires a 25.000MHz clock which is provided by X3. This clock is also an input to the FPGA (*ETH\_CLK*).

In the default configuration X4 is not fitted, and the clock for the Video DAC is intended to be generated by the logic inside the FPGA.

The clock for the USB PHY controller is provided by Y1, it is not used in this project.

• Serial interfaces

The *GR-XC3S-1500* provides two serial interfaces with standard SUB-D 9 pin female connectors, and RS232 line driver/receiver chips. The IC's implemented on board are capable of supporting data rates up to 1 M baud.

• Ethernet Interface

The *GR-XC3S-1500* board incorporates a Intel LXT971A 3.3V Dual-Speed Fast Ethernet PHY Transceiver device providing 10/100Mbit/s Ethernet interface, with RJ45 10/100Mbit Ethernet connector. To use this feature it is necessary to implement the Ethernet MAC function in the logic of the FPGA. Communication and data transfer between the MAC and PHY occurs over a standard MII interface. To utilize the Ethernet interface in a Leon system, appropriate driver software will be required depending on the features and operating system which the user wishes to implement.

#### • JTAG

Connector J9 allows a Xilinx Parallel Cable IV type ribbon cable (2x7pin 2mm connector) to be connected to the board. Alternatively connector J10 allows either flying leads or a low-cost JTAG programming cable such as the Digilent JTAG3 or USB type cables to be connected to the board. Both types of cable can be used with the Xilinx iMPACT software for programming of the Platform Configuration proms and for configuration of the FPGA.

# 2.3 LEON3 Design Configuration

The provided files by Gaisler Research which contains the VHDL model to be used could be "manually" modified in order to choose the features to be placed on the FPGA. However, a GUI xconfig tool which allows to configure the model is provided. The main window of the GUI configuration tool can be seen in figure 2.6 [3,6].

| LEON3MP Design Configuration |                |                              |

|------------------------------|----------------|------------------------------|

| Synthesis                    | Debug Link     | Save and Exit                |

| Clock generation             | Peripherals    | Quit Without Saving          |

| Processor                    | VHDL Debugging | Load Configuration from File |

| AMBA configuration           |                | Store Configuration to File  |

Figure 2.6. LEON3 GUI configuration tool

The GUI configuration tool can be accessed by executing the following command line on a cygwin (or Unix) bash shell, on the directory corresponding to the VHDL model template for the board (Leon\_VHDL\_model\Grlib-Leon3\grlib-gpl-1.0.17 -b2710\designs\leon3-gr-xc3s-1500):

\$ make xconfig

The GUI configuration tool allows to add or delete features of the VHDL model and set parameters for the synthesis and VHDL debugging. The set configuration is saved at a "config.vhd" file by clicking the "save and exit" button. The figures 2.7 and 2.8 shows the configuration windows for the processor and its peripherals, respectively.

| X Processor         |                                 |      |

|---------------------|---------------------------------|------|

|                     | Processor                       |      |

| 🔶 y 💠 n             | Enable LEON3 SPARC V8 Processor | Help |

| 1                   | Number of processors            | Help |

|                     | Integer unit                    |      |

| Floating-point unit |                                 |      |

|                     | Cache system                    |      |

|                     | мми                             |      |

|                     | Debug Support Unit              |      |

|                     | Fault-tolerance                 |      |

|                     | VHDL debug settings             |      |

| Main Men            | w <u>N</u> ext <u>F</u>         | rev  |

Figure 2.7. Processor configuration window

| 🗙 Peripherals |                                                |

|---------------|------------------------------------------------|

|               | Peripherals                                    |

|               | Memory controller                              |

|               | On-chip RAM/ROM                                |

|               | Ethernet                                       |

|               | IDE Disk controller                            |

|               | CAN                                            |

|               | UART, timer, I/O port and interrupt controller |

|               | Spacewire                                      |

|               | Keybord and VGA interface                      |

| Main Men      | u <u>N</u> ext <u>Prev</u>                     |

Figure 2.8. Peripherals configuration window

### 2.4 Procedure to place the processor on the FPGA

A design model containing the VHDL files of LEON3 for the GR-XC3S-1500 development board is provided by Gaisler. The available software tool to synthesize the provided files was the ISE® Foundation<sup>TM</sup> Package from Xillinx (version 9.2i) [7]. The ISE Foundation package is in the list of recommended software by the provider to perform the synthesis operation of the provided files.

The empirically "successful" procedure to place the correspondent .bit file on the FPGA is described by the following steps:

- Synthesize XST with the ISE 9.2i Project Navigator. The project is opened at the directory at the package provided by Gaisler Research: Leon\_VHDL\_model\Grlib-Leon3\grlib-gpl-1.0.17-b2710\designs\leon3-grxc3s-1500

- 2) On a cygwin bash shell and at the previously iundicated directory, the following command line is executed in order to perform the Place&Route in bash mode:

\$ make ise-map

3) After the Place&Route is successfully completed, the .\*bit file is generated by executing the following command line (on the same cygwin bash shell):

#### \$ make ise

After the .bit file is generated, it can be download to the FPGA with iMPACT (another program in the ISE Package) via JTAG cable. The \*.bit file download over the FPGA can be done from the iMPACT GUI. By this procedure the downloaded

FPGA configuration is lost every time the board is turned off. The same procedure can be done from the cygwin bash shell by executing the following command line:

\$ make ise-prog-fpga

The FPGA configuration PROMs can be programmed using the obtained \*.bit file by executing the following command on the cygwin shell window (the file is also downloaded via JTAG by this way):

\$ make ise-prog-prom

Downloading the .bit file into the PROMs configures the board to download automatically the file into the FPGA the \*.bit file configuration every time that it is turned on, making stand alone operation of the board possible.

A precompiled \*.bit file is also provided by Gaisler Research, it can be downloaded into the PROMs by ISE executing the following command in the cygwin bash shell (also via JTAG):

\$ make ise-prog-prom-ref

The results obtained with both \*.bit files are compared at the "test and results" section of this chapter.

## 2.5 The GRMON LEON Monitor

GRMON [4,5,6] is a debug monitor developed by Gaisler Research for the LEON Debug Support Unit (DSU), providing a non-intrusive debug environment on real target hardware. The LEON DSU can be controlled through any AHB master, and GRMON supports communications through the dedicated DSU UART or a PCI interface if available. GRMON can operate in two modes: stand alone or attached to gdb. Numerous commands are available to examine data, insert breakpoints and advance execution.

GRMON is used in stand alone mode during this project. LEON applications can be loaded and debugged using a command line interface in stand alone mode.

Some of the operations that are simplified using GRMON are listed as follows:

- Read/write access to all registers and memory

- Dissasembler and trace buffer management

- Downloading and execution of LEON applications

- Breakpoint and watchpoint management

- Auto-probing and initialization of LEON peripherals and memory settings

GRMON allows to access the LEON processor by several ways, in this project JTAG cable and parallel port (as set by default) were the only used. The following command line (in the GRMON installed directory) in a cygwin or Unix (DOS is also supported) bash shell is executed to initialize GRMON operation with JTAG cable:

\$ grmon -jtag

Several options can be used for GRMON initialization, as will be seen in further sections and chapters. An evaluation version of GRMON is included in the LEON software tools provided by Gaisler Research.

### 2.6 Tests and Results

The bit file obtained following the procedure described at the section 2.3 was by the methods also specified downloaded into the FPGA. The processor placed on the board was accessed with GRMON, despite some communication errors and a stack pointer warning, the GRLIB library components seemed to be correctly installed, as can be seen in figure 2.9.

| DCOM communication error, retrying warning: stack pointer not set | g                                 |

|-------------------------------------------------------------------|-----------------------------------|

| DCOM communication error, retrying                                | g                                 |

| DCOM communication error, retryin                                 | g                                 |

| Component                                                         | Vendor                            |

| LEON3 SPARC V8 Processor                                          | Gaisler Research                  |

| AHB Debug UART                                                    | Gaisler Research                  |

| AHB Debug JTAG TAP                                                | Gaisler Research                  |

| SVGA frame buffer                                                 | Gaisler Research                  |

| GR Ethernet MAC                                                   | Gaisler Research                  |

| ATA Controller                                                    | Gaisler Research                  |

| LEON2 Memory Controller                                           | European Space Agency             |

| AHB/APB Bridge                                                    | Gaisler Research                  |

| LEON3 Debug Support Unit                                          | Gaisler Research                  |

| Generic APB UART                                                  | Gaisler Research                  |

| Multi-processor Interrupt Ctrl                                    | Gaisler Research                  |

| Modular Timer Unit                                                | Gaisler Research                  |

| Keyboard PS/2 interface                                           | Gaisler Research                  |

| Keyboard PS/2 interface                                           | Gaisler Research                  |

| General purpose I/O port                                          | Gaisler Research                  |

|                                                                   | detailed report of attached cores |

Figure 2.9. Built LEON3 processor on GRMON monitor

Also some applications were successfully downloaded over RAM. However, it was not possible to execute the downloaded applications, not even a "hello world" test program. The obtained error message was "processor not in debug mode", making the board reset necessary to continue. The Flash memory related instructions were not possible to execute under these conditions. A failed attempt to access the registers is reported in figure 2.10.

| C:\Documents and Settings\agonzalez\Desktop\grmon-eval-1.1.32\grmon-eval\cygwin\grmo 🗆 🗙                    |

|-------------------------------------------------------------------------------------------------------------|

| apb: 80000600 - 80000700                                                                                    |

| DCOM communication error, retrying                                                                          |

| 04.01:01d Gaisler Research GR Ethernet MAC (ver 0x0)                                                        |

| ahb master 4, irq 12<br>apb: 80000b00 - 80000c00                                                            |

| edcl ip 192.168.0.51, buffer 2 kbyte                                                                        |

| 05.01:024 Gaisler Research ATA Controller (ver 0x0)                                                         |

| ahb master 5, irg 10                                                                                        |

| ahb: fffa0000 - fffa0100                                                                                    |

| Device 0: (None)<br>Device 1: (None)                                                                        |

| 00.04:00f European Space Agency LEON2 Memory Controller (ver 0x1)                                           |

| ahb: 00000000 – 20000000                                                                                    |

| ahb: 20000000 - 40000000                                                                                    |

| ahb: 4000000 – 8000000                                                                                      |

| apb: 80000000 - 80000100                                                                                    |

| 8-bit prom @ 0x0000000<br>01.01:006                                                                         |

| 01.01:006 Gaisler Research AHB/APB Bridge (ver 0x0)<br>ahb: 80000000 - 80100000                             |

| 02.01:004 Gaisler Research LEON3 Debug Support Unit (ver 0x1)                                               |

| ahb: 9000000 - a000000                                                                                      |

| 01.01:00c Gaisler Research Generic APB UART (ver 0x1)                                                       |

| irg 2                                                                                                       |

| aph: 80000100 - 80000200                                                                                    |

| DCOM communication error, retrying<br>baud rate 5000000                                                     |

| 02.01:00d Gaisler Research Multi-processor Interrupt Ctrl (ver 0x3)                                         |

| apb: 80000200 - 80000300                                                                                    |

| 03.01:011 Gaisler Research Modular Timer Unit (ver 0x0)                                                     |

| irg 8                                                                                                       |

| aph: 8000300 - 80000400                                                                                     |

| 8-bit scaler, 2 * 32-bit timers, divisor 40<br>04.01:060 Gaisler Research Keyboard PS/2 interface (ver 0x1) |

| ing 4                                                                                                       |

| apb: 80000400 - 80000500                                                                                    |

| 05.01:060 Gaisler Research Keyboard PS/2 interface (ver 0x1)                                                |

| irg 5                                                                                                       |

| aph: 80000500 - 80000600                                                                                    |

| 08.01:01a     Gaisler Research   General  purpose  I/O  port  (ver  0x0)<br>apb:  80000800 –  80000900      |

| grlib> reg                                                                                                  |

| DCOM communication error, retrying                                                                          |

| DCOM communication error retruing                                                                           |

| Cannot continue, processor not in debug mode                                                                |

| DCOM communication error, retrying<br>Cannot continue, processor not in debug mode                          |

| Cannot continue, processor not in debug mode                                                                |

| psr: 00000000 wim: 00000000 tbr: 00000000 y: 00000000                                                       |

| DCOM communication error, retrying                                                                          |

|                                                                                                             |

| pc: 00000000 unimp DCOM communication error, retrying                                                       |

|                                                                                                             |

| npc: 00000000 unimp DCOM communication error, retrying                                                      |

|                                                                                                             |

|                                                                                                             |

|                                                                                                             |

| grlib>                                                                                                      |

|                                                                                                             |

Fiugre 2.10. Failures on the built processor

The bitgen report and Place&Route report files presented several warnings but almost all of them were related to the USB port devices.

After the reported results, the precompiled bitfile provided by Gaisler Research was downloaded on the FPGA. No communications errors or stack pointer warnings appeared in that case, as can be seen in figure 2.11.

| 🚳 Command Prompt - grmon-eval -nb -jta                                                                                                                                                                                                                                                                                                                                                                 | g                                                                                                                                                                                                                                                                                                                                                                                   | - 🗆 X |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| initialising<br>detected frequency: 40 MHz                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                     |       |

| Component<br>LEON3 SPARC U8 Processor<br>AHB Debug UART<br>AHB Debug JTAG TAP<br>SUGA frame buffer<br>GR Ethernet MAC<br>USB Debug Comm. Link<br>ATA Controller<br>LEON2 Memory Controller<br>AHB/APB Bridge<br>LEON3 Debug Support Unit<br>Generic APB UART<br>Multi-processor Interrupt Ctrl<br>Modular Timer Unit<br>Keyboard PS/2 interface<br>Keyboard PS/2 interface<br>General purpose I/O port | Vendor<br>Gaisler Research<br>Gaisler Research<br>Gaisler Research<br>Gaisler Research<br>Gaisler Research<br>Gaisler Research<br>Gaisler Research<br>European Space Agency<br>Gaisler Research<br>Gaisler Research<br>Gaisler Research<br>Gaisler Research<br>Gaisler Research<br>Gaisler Research<br>Gaisler Research<br>Gaisler Research<br>Gaisler Research<br>Gaisler Research |       |

| Use command 'info sys' to print a<br>grlib>                                                                                                                                                                                                                                                                                                                                                            | a detailed report of attached cores                                                                                                                                                                                                                                                                                                                                                 | -1    |

Figure 2.11. Precompiled LEON3 processor on GRMON monitor

Operations over the registers, and applications download (into RAM and Flash) and execution were successfully completed under these conditions.

After the obtained results and a relatively high time investment to solve the problems of the "manually" generated processor, and after analyzing the possible problem causes such as the ISE version used, it was decided to continue the board testing using the precompiled processor. The possibility of physical damages on the board was dismissed since it was possible to run on it the precompiled processor.

The LEON3 VHDL model flexibility cannot be discarded by the obtained results, but it neither cannot be proved due to the choice of continue the project using the precompiled version. However, the LEON3 processor reliability for the support of an embedded operating system was possible to test by the procedures performed in the following chapter. The fully-operative processor version allowed to continue with the project's next step.

# **Chapter 3**

## **Firmware Implementation**

This chapter explains the procedure to place an Operating System on the Board, after the processor has been installed.

### **3.1 The SnapGear Linux**

SnapGear Linux is a full source package provided by Gaisler. It contains kernel, libraries and application code for rapid development of embedded Linux systems. MMU and non-MMU Leon configurations are supported. A single cross compilation toolchain is provided, which is capable of compiling the kernel and applications for any configuration.

The Linux kernel can be configured using a graphical interface. Drivers and features can be removed in order to save space. On LEON3 systems the AMBA plug&play information is used to detect devices and load their respective software drivers.

A small boot loader is incorporated into the SnapGear Linux software distribution, it is specially designed for LEON processors. Its main propose is initialize basic hardware, such as memory controllers and console output for debugging, before launching LEON Linux.. The boot loader is stored in a non-volatile memory at the address where the LEON processor reads first its instructions to be executed, usually stored in flash at address 0.

Supported hardware on the latest version is presented in the following list.

New hardware is being added costantly:

- LEON2, with or without MMU, FPU, MUL/DIV.

- LEON3, with or without MMU, FPU, MUL/DIV.

- LEON3 multi processor systems, SMP

- APBUART

- GPTIMER

- GRETH 10/100 and Gbit

- OpenCores 10/100 Ethernet MAC

- SMC91x 10/100 Ethernet MAC

- APBPS2

- APBVGA

- GRUSBHC

- GRVGA

- ATACTRL

- GRPCI

- GRETH over PCI

- GR/OpenCores

## 3.2 SnapGear Linux Compiling

The SnapGear Linux compiling processes was completed successfully in a Unix host. Several problems appeared using cygwing, so it was discarded.

The procedure to compile SnapGear Linux is composed by the following steps:

- 1) Installing the toolchain

- 2) Installing the SnapGear distribution

- 3) Configuring Linux

- 4) Building SnapGear

The indicated steps are described as follows:

### **3.2.1** Installing the Toolchain

Before compile SnapGear Linux, a toolchain able to compile LEON SPARC Linux binaries must be chosen, it was selected the sparc-linux-3.4.4 toolchain. The chosen toolchain was installed in the host's /opt directory. After being installed, the toolchain was added to the PATH variable using the following command line:

\$ export PATH=\$PATH:/opt/sparc-linux-3.4.4/bin

After installing the toolchain it is possible to cross compile applications for SPARCC LEON Linux, as indicated by the following command line (the brackets are representative):

\$ sparc-linux-gcc -o [executable name] [source file name .c]

The following command line demonstrates that the output binary is a SPARC binary:

\$ file [executable name]

Obtaining the following output message (for an executable file named "args"):

args: ELF 32-bit MSB executable, SPARC, version 1 (SYSV), dynamically linked (uses shared libs), not stripped

### 3.2.2 Installing the SnapGear Distribution

The provided SnapGear distribution is compressed with tar and bunzip2, its installation on the Linux host in use can be done by executing the following command line (xx and yy values depends on the version).

\$ tar -xjf snapgear-xx-yy.tar.bz2

### 3.2.3 Configuring Linux

The SnapGear distribution includes an easy to use graphical interface (GUI). From the GUI is possible to select processor, Linux version, C library and what applications will be include into the root file system (ROMFS image) accessed by Linux during run time. Is also possible to configure the boot loader parameters and configure the Linux kernel.

The configuration GUI can be invoked by executing the following command line in the SnapGear distribution installed directory:

\$ make xconfig

The GUI main window can be seen in figure 3.1.

Figure 3.1. SnapGear main configuration GUI

A template configuration for the board is also included, this can be set by clicking the "Template Configuration" button on the GUI, then choosing it (GR-XC3s-1500) in the window that appears and activating the update configurations option, as shown in figure 3.2.

| X Template Configurations                                                             |          |

|---------------------------------------------------------------------------------------|----------|

| Template Configurations                                                               |          |

| gr_xc3s_1500 Templates for leon3mmu                                                   | Help 🛆   |

| $  \diamond y   \diamond -   \diamond n  $ Update configurations with above selection | Help     |

| Main Menu <u>N</u> ext <u>P</u> re                                                    | <b>v</b> |

Figure 3.2. Template Configuration selection

By activating the "Update configurations with above selection" option, the launch of the GUIs for the configuration of the kernel and other settings are suspended, and all the settings are configured as indicated in the chosen template. However, as it can be seen in figure 3.1, there is also an option for load a configuration from a file, so the board template configuration and customized settings can be mixed.

In this project, the activation of the template for the GR-xc3s-1500 Board was considered enough. This selection was compatible with the modifications over the Linux kernel indicated at the section 3.3 (Modifications over the SnapGear Kernel).

However, desired changes can be performed by setting the provided options by clicking other two buttons on the GUI, Vendor/Product Selection and Kernel/Library/Defaults Selection. The application selection menus obtained for each buttons are shown on figures 3.3 and 3.4.

| Vendor/Product Selection                   |                                       |                                     |        |  |  |

|--------------------------------------------|---------------------------------------|-------------------------------------|--------|--|--|

|                                            | Vendor/Product Selection              |                                     |        |  |  |

|                                            | Select the Vendor you wish to target  |                                     |        |  |  |

| gaisler                                    | Vendo                                 | r                                   | Help   |  |  |

|                                            | Select the Product you wish to target |                                     |        |  |  |

| LITE                                       | Snap Ge                               | ar Products                         | Help   |  |  |

| leon3mm                                    | u ga                                  | gaisler Products Help               |        |  |  |

| <br>^ leon2                                |                                       | Select the options for a selected P | roduct |  |  |

| leon2m                                     | nmu                                   | Gaisler/Leon2/3/mmu options         |        |  |  |

| <ul><li>◆ leon3</li><li>◆ leon3m</li></ul> | nmu                                   | <u>N</u> ext P                      | rev    |  |  |

Figure 3.3. Vendor/Product section

Figure 3.4: kernel/library/defaults selection menu

Changes in this options are not saved if a template has been selected as previously indicated, but a template can be used if the button "load configuration from file" is used. Some of the allowed features to modify are presented as follows:

- Processor Type and MMU

- C library

- Kernel version

- Configuring the boot loader

- Configuring the Linux 2.6.x kernel (MMU, i.e. only LEON3)

- Configuring the Linux 2.0.x kernel (no MMU)

Special GUI configurations utilities are provided for the both kernels, however, them do not perform automatically changes needed as a consequence of eventual modifications made by the user, leading to possible errors on the compiling process. The GUI configuration utility for the Linux 2.6.x case is shown on figure 3.5.

Figure 3.5. Linux 2.6.x kernel GUI configuration utility

It was considered to use a JFFS2 file system on flash memory but many compilation problems appeared and many files seemed to be necessarily (without help of the GUI) modified. Similar problems appeared trying to configure the USB port in order to manage an external memory device. The kernel GUI configuration was not very useful in those cases. However the data storage on the board was not considered a critical issue, since it is also possible to transmit data immediately after it is processed.

Actual changes on the kernel were performed on some files without the help of the previously described GUI, as it can be seen on section 3.3.

### 3.2.4 Building SnapGear

The Linux SnapGear compilation is executed by the "make" command, as indicated in the following line in the SnapGear distribution installed directory:

\$ make

The generated images can be found at the /images subdirectory. Information about the compiling times can be found at the section 3.5 (Tests and Results).

### **3.3** Modifications over the SnapGear Linux Kernel

Some changes were performed over the Kernel in order to set the following parameters:

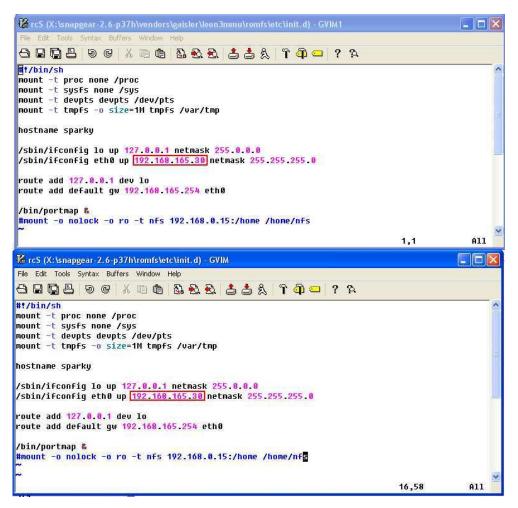

#### 3.3.1 Board IP address

As previously said, the Board's Ethernet port was chosen to test the communication with external stages. The following files were modified indicating the Board new IP address:

- vendors/gaisler/leon3mmu/romfs/etc/init.d/rcS

- romfs/etc/init.d/rcS

Both files contain the same information, as shown on figure 3.6. The assigned IP address for the Board was 192.168.165.30 (as also indicated on figure 3.6).

Figure 3.6. Board IP address setting

Is important to notice that the directory /romfs is created during the kernel first compilation. However, if /romfs and some subdirectories are manually created them will not be overwritten. Only missing directories and default settings will be added during the compilation process.

#### 3.3.2 Adding programs to be executed on the board

The executable files of the programs to be executed on the Board must be add to the /romfs directory. By doing this, the programs will be found at the SnapGear root file system during its execution. The same procedure can be performed to place any file or subdirectory wanted in the root file system during SnapGear execution.

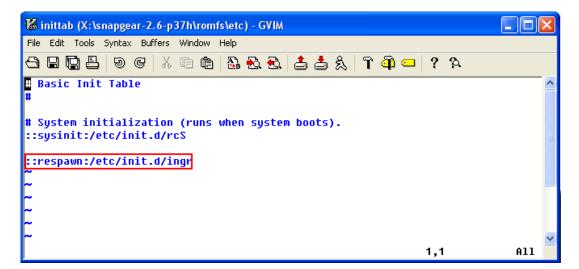

### 3.3.3 Automatic Program Startup

A program can be set to automatically run at the SnapGear startup. One way to do this is by modifying (or creating) the "inittab" file before compile the Kernel. inittab shall be placed at the romfs/etc directory.

The inittab[] file describes which processes are started at boot and during normal operation. An example of inittab is shown in figure 3.7

Figure 3.7. Example of the inittab file

The "sysinit" action, set as default, indicates to load the configuration at the rcS file. The "respawn" action was added to run the "ingr" program at startup and whenever it terminates. The call to run the SnapGear console shell has been eliminated in the shown example.

Other actions can be called besides sysinit and respawn, but are not needed in this project. As can be presumed, a wrong configuration of the inittab file can make totally inoperative the operating system.

### **3.4 SnapGear Linux Installing Procedure**

After the Kernel compilation has been completed, the obtained images can be found at the /images directory. The image.flashbz file is the appropriate one to use, since it can be stored in Flash memory and contains a complete boot loader.

The chosen procedure to place image.flashbz in the processor's Flash memory was using the GRMON monitor via JTAG cable. GRMON is invoked on the server as indicated in the following command line:

\$ grmon-eval -nb -jtag

The –nb option allows Linux to take care of traps instead of having GRMON to stop the execution. After verify the processor operation the flash memory shall be erased, as indicated by the following execution line on grmon:

GRMON> flash erase all

Then, the image can be loaded into Flash memory:

GRMON> flash load image.flashbz

After the download is completed, SnapGear can be executed by pressing the board's reset button or executing the following line:

GRMON> run 0

As previously said, for the chosen Kernel configuration SnapGear will run on the serial port 1 of the board, at 38400 baud. By the described procedure SnapGear will run in stand alone operation each time the Board is turned on or reset. The next section explains the details the about SnapGear usage.

### 3.5 Tests and Results

The compiling times for SnapGear were measured for the previously indicated configuration (immediately after execute the make command). If the SnapGear distribution in use is compiled by first time, it takes around 5 minutes. If it is recompiled it takes around 40 seconds, since are used almost all the files built for the first compilation, despite eventual minor changes on the kernel (such as the indicated in the section 3.3).

The downloading time for the image on the Board Flash memory was also measured, registering around 15 minutes, the download speed was 24.8 Kbit/s as can be seen in figure 3.8. The erasing of the flash memories (a step previous to the image download) takes around 2 minutes.

| Command Prompt -                                                                |                                                                  |           |

|---------------------------------------------------------------------------------|------------------------------------------------------------------|-----------|

| rlib> flash load<br>ection: .text at f<br>otal size: 273624<br>ead 37 symbols   | lmage25062.flash                                                 | bz        |

| otal size: 273624                                                               | butes (24.8 kh                                                   | it/s)     |

| ead 37 symbols                                                                  |                                                                  |           |

| ntry point: 0x000                                                               | เออออ                                                            |           |

| ntry point: 0x000<br>rlib> flash erase<br>rase in progress<br>lock @ 0x00000000 | all                                                              |           |

| lock C 0x00000000                                                               | : code = 0x80                                                    | ок        |

| lock C 0x00020000                                                               | : code = 0x80                                                    | ŐŘ        |

| lock @ 0x00040000                                                               |                                                                  | OK        |

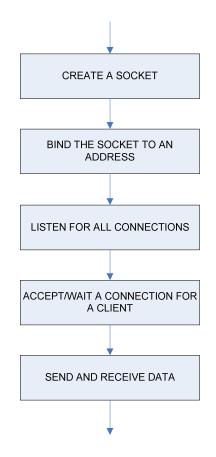

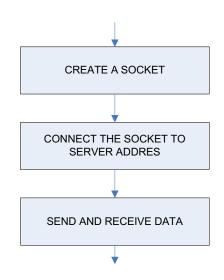

| lock @ 0x00060000<br>lock @ 0x00080000                                          |                                                                  | OK<br>OK  |

| lock @ 0x000a0000                                                               |                                                                  | OK        |

| lock @ 0x000c0000                                                               | : code = 0x80                                                    | OK .      |

| lock @ 0x000e0000                                                               | $: code = 0 \times 80$                                           | OK        |

| lock C 0x00100000<br>lock C 0x00120000                                          |                                                                  | OK<br>OK  |

| lock @ 0x00120000                                                               | code = 0x80                                                      | OK<br>OK  |

| lock @ 0x00160000                                                               | $code = 0 \times 80$                                             | ŎK .      |

| lock @ 0x00180000                                                               |                                                                  | OK        |

| lock @ 0x001a0000<br>lock @ 0x001c0000                                          |                                                                  | OK<br>OK  |

| lock @ 0x001c0000                                                               | : code = 0x80                                                    | OK<br>OK  |

| lock @ 0x00200000                                                               | : code = 0x80                                                    | OK        |

| 10cl 0 0v00220000                                                               | code = 0x80                                                      | <u>ok</u> |

| lock @ 0x00240000                                                               | : code = 0x80<br>: code = 0x80<br>: code = 0x80<br>: code = 0x80 | OK        |

| lock @ 0x00260000<br>lock @ 0x00280000                                          | = code = 0x80                                                    | OK<br>OK  |

| lock C 0x002a0000                                                               | : code = 0x80                                                    | OK        |

| lock @ 0x002c0000                                                               | : code = 0x80                                                    | OK        |

| lock @ 0x002e0000                                                               | : code = 0x80                                                    | OK        |

| lock C 0x00300000<br>lock C 0x00320000                                          |                                                                  | OK<br>OK  |

| lock @ 0x00320000<br>lock @ 0x00340000                                          |                                                                  | OK OK     |

| lock @ 0x00360000                                                               | : code = 0x80                                                    | OK        |

| lock @ 0x00380000                                                               | $code = 0 \times 80$                                             | OK        |

| lock @ 0x003a0000<br>lock @ 0x003c0000                                          | : code = 0x80<br>: code = 0x80                                   | OK<br>OK  |

| lock @ 0x003e0000                                                               | code = 0x80                                                      | OK        |

| lock @ 0x00400000                                                               | : code = 0x80                                                    | OK        |

| lock @ 0x00420000                                                               | $code = 0 \times 80$                                             | OK        |

| lock @ 0x00440000<br>lock @ 0x00460000                                          | : code = 0x80<br>: code = 0x80                                   | OK<br>OK  |

| lock @ 0x00480000                                                               | code = 0x80                                                      | OK CK     |

| lock @ 0x004a0000                                                               | : code = 0x80                                                    | OK        |

| lock @ 0x004c0000                                                               |                                                                  | OK        |

| lock @ 0x004e0000<br>lock @ 0x00500000                                          | : code = 0x80<br>: code = 0x80                                   | ок<br>ок  |

| lock @ 0x00520000                                                               | code = 0x80                                                      | OK<br>OK  |

| lock @ 0x00540000                                                               | : code = 0x80                                                    | OK        |

| lock @ 0x00560000                                                               |                                                                  | OK        |

|                                                                                 | : code = 0x80<br>: code = 0x80                                   | OK<br>OK  |

| lock @ 0x005c0000                                                               | code = 0x80                                                      | OK<br>OK  |

| lock @ 0x005e0000                                                               | : code = 0x80                                                    | OK        |

| lock @ 0x00600000                                                               |                                                                  | OK        |

| lock © 0×00620000<br>lock © 0×00640000                                          |                                                                  | OK<br>OK  |

| lock @ 0x00660000                                                               | code = 0x80                                                      | OK<br>OK  |

| lock @ 0x00680000                                                               | : code = 0x80                                                    | OK        |

| lock @ 0x006a0000                                                               | : code = 0x80                                                    | OK        |